受益晶圆扩产:先进封装主流路线及厂商梳理

一. 半导体封装

半导体制造分为芯片设计、晶圆制造、封装测试三大环节。

封装是将前道产出的裸芯片(Die)封装为标准化成品,再完成后续功能、可靠性测试,确保芯片符合出厂要求。

(1)封装目的:机械保护(避免外界环境损伤)、电气连接(芯片与PCB互连)、散热管理(导出芯片热量)。

(2)工艺步骤:晶圆减薄→晶圆切割→芯片贴装→引线键合→塑封保护→切筋成型。

(3)传统封装类型:DIP(双列直插封装)、QFP(四方扁平封装)、BGA(球栅阵列封装)。

二. 先进封装概览

随着2nm工艺突破,晶体管制程已接近物理极限,先进封装成为了提升芯片性能提升的新路径:

其本质是通过多芯片集成、高密度互连、异质整合等方式,实现更高性能密度、更高带宽、更低功耗。

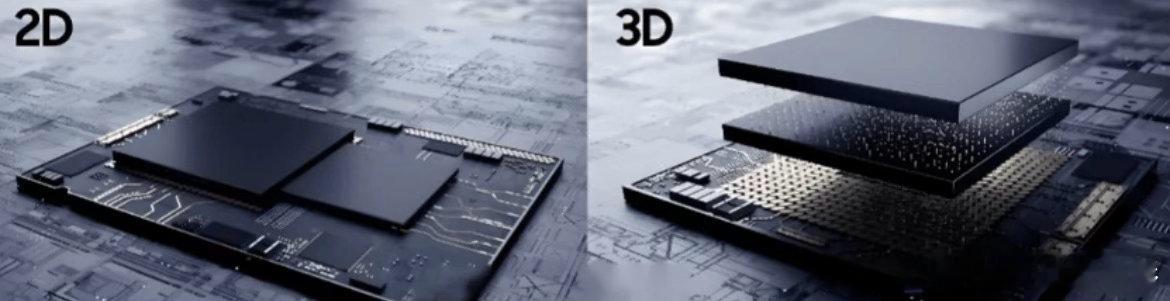

2.1 与传统二维封装的区别

(1)三维集成:通过TSV、RDL等技术,实现芯片横向集成(2.5D)或垂直堆叠(3D),缩短互连长度。

(2)异质集成:将不同工艺节点、材料、功能的芯片(如GPU、HBM)封装在同一模块,实现系统级功能。

2.2 核心底层技术

(1)倒装焊(FC):芯片有源面朝下,通过微凸块与基板互连,缩短互连路径。

(2)重布线层(RDL):在芯片表面重新布线,将芯片焊盘重新分布为阵列式凸块,实现更高密度互连。

(3)硅通孔(TSV):在芯片中介层刻蚀垂直通孔,并填充金属材料,实现层间电气连接。

(4)中介层(Interposer):高密度布线的半导体层,连接逻辑芯片与内存(2.5D)。

(5)混合键合:将铜焊盘直接键合,无需焊球,实现更高的键合密度。

三. 先进封装主流路线

3.1 2.5D封装

(1)核心:通过硅中介层在同一平面实现多芯片互连,不做垂直堆叠,适配高端AI芯片与HBM内存的高带宽需求。

(2)代表路线:台积电CoWoS、英特尔EMIB、三星I-Cube。

3.2 3D封装

(1)核心:通过TSV或混合键合实现多芯片垂直堆叠,大幅缩短互连路径,并进一步提升集成度。

(2)代表路线:台积电SoIC、英特尔Foveros、三星X-Cube。

3.3 其他类型

(1)系统级封装(SiP):将不同功能的芯片集成在单个封装体,用于消费电子、汽车电子、物联网等场景。

(2)晶圆级封装(WLCSP):直接在晶圆上完成封装,体积极小,分为扇入型(Fan-in)、扇出型(Fan-out),用于轻薄化消费电子。

四. 先进封装市场格局

晶圆IDM大厂商凭借前道工艺优势主导高端市场:台积电(台)、三星(韩)、英特尔(美)。

第三方封测厂(OSAT)凭借量产规模、客户资源及工艺经验跟进布局:日月光ASE(台)、安靠Amkor(美)、力成科技(台)等。

长电科技:全球第三、大陆第一大封测企业,覆盖先进封装全栈技术,客户包括高通、博通、SK海力士、长存等。

通富微电:全球第四、大陆第二大封测企业,深度绑定AMD,承接其80%的芯片封测订单。

华天科技:大陆第三大封测企业,构建全球化多基地布局,覆盖消费电子、汽车电子、存储等多场景,客户结构分散。

盛合晶微:主营中段硅片加工、晶圆级封装(WLP)、芯粒多芯片集成封装等先进封测服务。

甬矽电子:专注高端先进封装业务,覆盖Bumping、FC、SiP、WLP、QFN/DFN等封装类型。