新的研究针对“超越硅”的发展方向,对一系列二维(2D)栅极堆栈集成方法展开了测试。首尔国立大学(SNU)的一个研究团队精心概述了“栅极堆栈”工程的路线图,而这一工程是二维晶体管的核心技术所在。此项研究成果于2025年9月11日发表在《自然电子》杂志上。

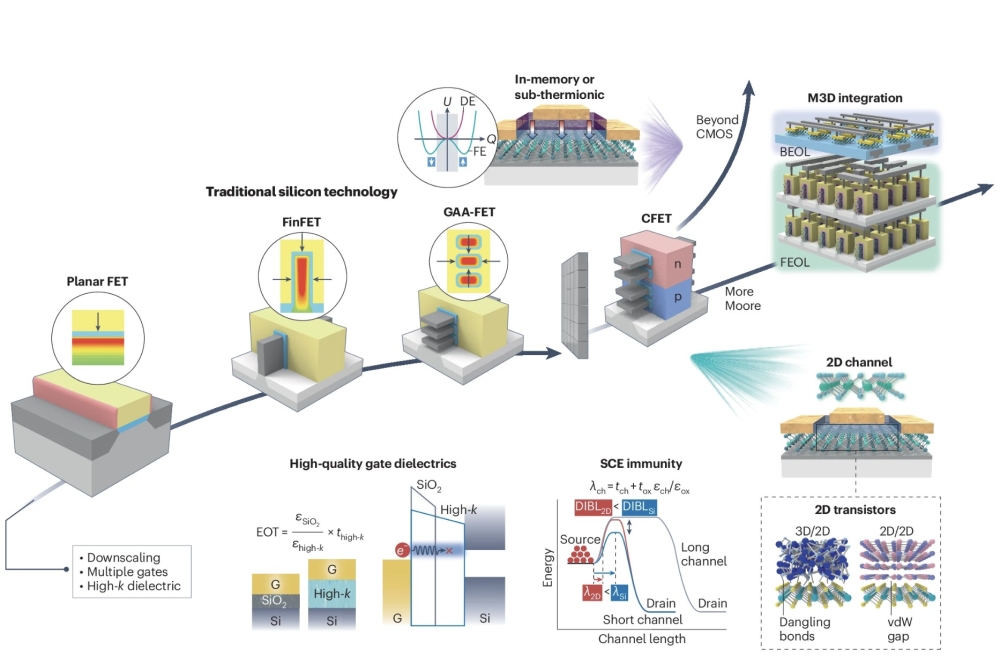

数十年来,互补金属氧化物半导体(CMOS)技术有力地推动了性能提升与集成密度增长。然而,进一步的技术缩放正日益受到物理和静电限制的掣肘。二维半导体作为一种“超越硅”的解决方案,正吸引着与日俱增的关注目光。诸如三星电子、台积电、英特尔、艾梅克(Imec)等芯片企业及研究机构,已将二维半导体晶体管纳入2030年代中期以后的下一代技术发展蓝图。

随着大量研发项目如火如荼地开展,二维半导体正从长期展望转变为迅速崛起的下一代核心技术。但这并非一个轻而易举的过渡阶段,“栅极堆栈”集成技术堪称二维半导体商业化进程中的重大阻碍。栅极堆作为控制静电通道导通的关键结构,其质量优劣直接决定了器件的性能与稳定性。然而,若将现有的硅晶体管工艺直接应用于二维半导体,不仅会降低介质质量,还会引发界面缺陷、漏电流等诸多问题。故而,开发适配二维界面的新材料与工艺集成,被视作实现二维半导体商业化的最为关键的任务。

在近期发表的这篇论文中,首尔大学工程学院电气与计算机工程系的Chul - Ho Lee所领导的研究团队,深入分析了各类门栈集成方法,并依据性能指标对其进行了定量基准测试,旨在为未来技术发展方向勾勒清晰轮廓。

首先,研究将栅极堆栈集成方法细致地划分为五类:(1)范德华(vdW)介质;(2)vdW氧化介质;(3)准vdW介质;(4)vdW种子介质;(5)非vdW种子介质。每种方法均依据界面陷阱密度、等效氧化物厚度、栅极泄漏密度、阈值电压和电源电压等指标进行评估。该团队参照国际设备和系统路线图(IRDS)中所明确的目标,对这些指标进行了基准测试。这一过程催生了一个系统的发展路线图,为学术界和工业界提供了极具价值的参考依据。

研究团队还展示了结合铁电材料的栅极堆在下一代设备中的应用潜力。例如,借助铁电嵌入门堆栈,能够实现超低功耗逻辑、非易失性存储器和内存计算等功能。此外,研究人员还着重概述了实际应用要求,涵盖后端线(BEOL)兼容性、低温沉积(< 400°C)、晶圆级均匀性和长期可靠性等方面。这充分凸显了超越理论探讨的现实工业适用性。

这项研究不仅证实了超低功耗、高性能晶体管的可行性,还提出了兼顾未来单片3D集成和后端线兼容工艺的具体技术方向。此外,本次研究的技术有望成为推动人工智能(AI)半导体、超低功耗移动芯片、超高密度服务器等下一代信息通信技术(ICT)基础设施发展的关键动力。

永霖光电-UVSIS-UVLED紫外线应用专家-独家发布